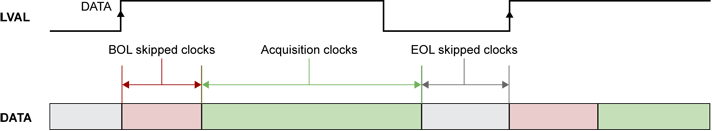

LVAL Timing Diagram

When the board is configured for image acquisition from an area-scan camera or from a line-scan camera:

- The rising edge of LVAL is actually the reference for the horizontal timing

- The falling edge of LVAL is ignored

LVAL timing diagram

If, at the rising edge of LVAL, the acquisition of the next line is enabled, the board

- Skips a pre-defined amount (HsyncAft_Tk) of camera clock cycles at begin of line (BOL)

- Acquires a pre-defined amount (Hactive_Px) pixel data

- Terminates the line acquisition

The subsequent clock cycles are skipped until a new LVAL rising edge occurs.

You can configure the frame grabber to use the DVAL signal as a clock qualifier but this feature is rarely used. Therefore, the default configuration ignores the DVAL signal.

Applicable limits

Parameter |

Min |

Typ |

Max |

Unit |

LVAL high duration |

1 |

# clocks with active video |

N/A |

Qualified clock cycle |

LVAL low duration |

1 |

# clocks with blanked video |

N/A |

Qualified clock cycle |

Skipped clocks at begin of line (BOL) |

0 |

0 |

255 |

Qualified clock cycle |

Acquired pixels |

Refer to Hactive_Px |

- |

Refer to Hactive_Px |

Pixels |

Skipped clocks at end of line (EOL) |

0 |

- |

N/A |

Qualified clock cycle |

EOL skipped clocks |

Others: 0 |

- |

N/A |

Qualified clock cycle |

A qualified clock cycle is defined as:

- Any clock cycle when the frame grabber is configured to ignore DVAL.

- A clock cycle with DVAL = 1 when the frame grabber is configured to use DVAL.

When DVAL is enabled:

- The data acquisition is inhibited for clock cycles where DVAL = 0. Only the data corresponding to DVAL = 1 are effectively acquired.

- The BOL skipped clock counter is not incremented for clock cycles where DVAL = 0. In other words, HsyncAft_Tk specifies the amount number of "clock cycles with DVAL = 1" to skip at begin of line.