Open Emitter Digital Output Mode

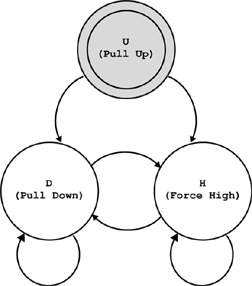

To be used as open emitter digital output, the circuit is either in State H (Force High) or in State D (Force Low) according to the applied digital level:

Applied digital level |

Output State |

HIGH |

State H (Force High) |

LOW |

State D (Pull Down) |

A state transition from State U (Pull-Up) occurs when setting IOE output mode after power ON or FPGA boot sequence.

In State D (Pull Down), the input is tied to the IGND through a 2 kΩ pull-down resistor.

Multiple open emitter digital outputs can be tied together.

Open emitter digital output state